The collaboration signals Red Hat’s growing commitment to open architectures, bringing enterprise Linux to the RISC-V ecosystem.

Red Hat has officially announced a strategic partnership with SiFive, a pioneer in RISC-V processor design, to release the developer preview of Red Hat Enterprise Linux 10 (RHEL 10) on the SiFive HiFive Premier P550 platform. This marks Red Hat’s first major step toward supporting the fast-growing RISC-V architecture in enterprise environments.

Developers will be able to download the binary image and Linux 6.12 kernel source code with RISC-V support starting June 1, 2025.

What is RISC-V and Why It Matters

RISC-V is an open standard instruction set architecture (ISA) based on reduced instruction set computing (RISC) principles. Unlike proprietary architectures such as x86 or ARM, RISC-V is royalty-free, allowing companies to build fully customized, low-cost, and power-efficient processors.

RISC-V is already being adopted in consumer electronics, edge computing, embedded systems, and even data center applications. As open-source hardware gains momentum, Red Hat’s move into this space highlights the growing demand for flexible, vendor-neutral alternatives.

Red Hat’s Commitment to Open Hardware

Traditionally focused on x86 and ARM platforms, Red Hat’s decision to support RISC-V with RHEL 10 underscores a significant strategic shift.

“Offering RHEL on RISC-V is not just a technical milestone, it’s a commitment to the principles of openness and community-driven innovation,” said a Red Hat spokesperson.

Red Hat aims to achieve two key goals with this developer preview:

- Enable customers to evaluate RISC-V for enterprise workloads, edge deployments, and embedded solutions.

- Stimulate development by providing early access to the Linux kernel and system tools needed to build production-grade RISC-V solutions.

Built on CentOS Stream 10: Full Transparency and Community Access

The developer preview is based on CentOS Stream 10, and Red Hat is making the RISC-V source code available through the CentOS ISA Special Interest Group (SIG). This ensures full alignment with Red Hat’s open development model and provides developers with a stable and transparent platform for experimentation and contribution.

The SiFive HiFive Premier P550: A Developer-Friendly RISC-V Platform

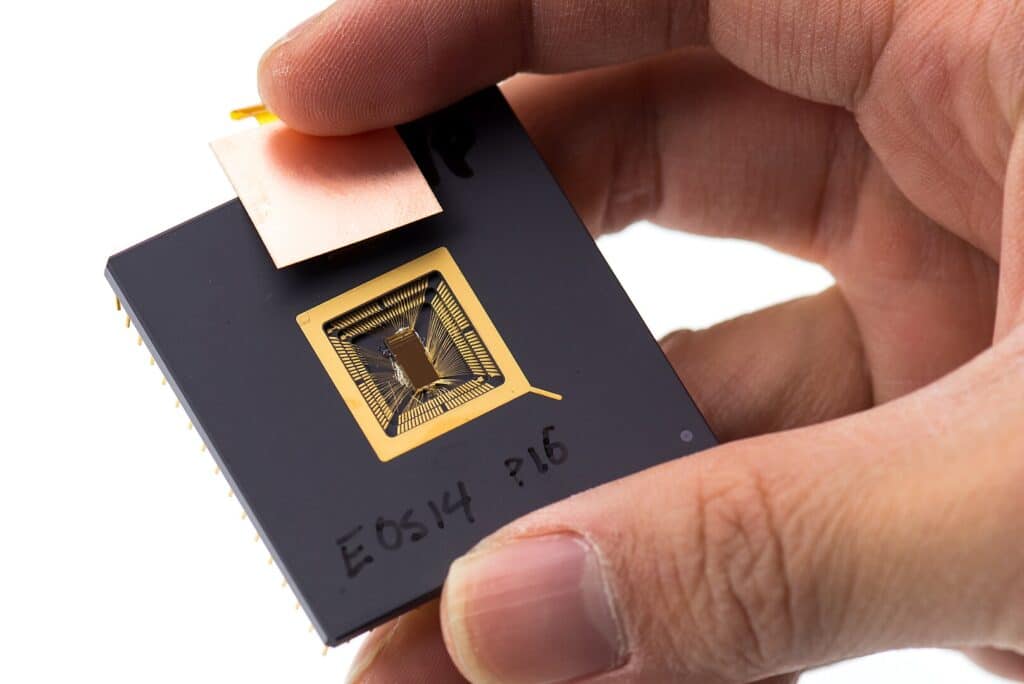

The preview is optimized for the SiFive HiFive Premier P550, a high-performance RISC-V development board. It offers a reliable and accessible path for developers looking to test RHEL 10 on real RISC-V hardware.

The P550 is designed for use cases in IoT, edge computing, and light server workloads, making it ideal for organizations interested in evaluating RISC-V for production scenarios.

Availability and What’s Next

The RHEL 10 developer preview for RISC-V will be available for public download starting June 1, 2025, through the Red Hat developer portal. The package will include:

- Binary ISO image for the SiFive P550

- Linux 6.12 kernel source with RISC-V support

- CentOS Stream 10 source packages

“RISC-V is more than an emerging trend—it’s the next phase of hardware evolution. We want open source software to be at its foundation,” said Red Hat.

Developers, enterprises, and embedded system integrators are encouraged to test the preview, submit feedback, and contribute to shaping the future of enterprise Linux on RISC-V.

Final Thoughts

By embracing RISC-V early in its enterprise journey, Red Hat is positioning itself as a leader in open hardware and software convergence. The collaboration with SiFive demonstrates the powerful synergy between open-source communities and next-generation chip design.

With this move, Red Hat not only extends its influence into new hardware territory but also reaffirms its role in guiding the future of modular, transparent, and high-performance computing across architectures.